# MAX77752 Programmer's Guide

UG6627; Rev 0; 3/18

# Abstract

This programmer's guide complements the data sheet for the MAX77752. Whereas the data sheet provides detailed descriptions of the MAX77752 hardware and electrical specifications, this document focuses on register descriptions and provides general advice for programmers

Maxim Integrated Page 1 of 83

# **Table of Contents**

| Overview                                                       | 7  |

|----------------------------------------------------------------|----|

| Reset Values                                                   | 8  |

| Global Resources                                               | 9  |

| Register Reset Conditions                                      | 9  |

| SYS Undervoltage Lockout Comparator (SYSUVLO_F_I)              | 9  |

| System Reset Comparator (SYSRSTTH and SYSRSTHYS)               | 9  |

| System Brownout Comparator (SYSBO)                             | 9  |

| Thermal Monitor (TOLVD)                                        | 10 |

| Chip Identification (CID)                                      | 10 |

| PGOOD Output (PG_DLY)                                          | 10 |

| Low Power (OTP_PHUP_1)                                         | 11 |

| LP_MODE Input                                                  | 11 |

| LP_REQ Output (OTP_INT_PU and ALT_LP_REQ)                      | 11 |

| LP_ACK Input (OTP_LPACK_POL)                                   | 12 |

| WP_L Output                                                    | 12 |

| External Regulator Enable/Disable Control                      | 12 |

| External Regulator Enable/Disable Outputs (EREG_EN1, EREG_EN2) | 13 |

| EREG_POK Input                                                 | 13 |

| On/Off Controller                                              | 15 |

| Hiccup Count Algorithm                                         | 18 |

| Flexible Power Sequencer                                       | 18 |

| Masters                                                        | 20 |

| Available Resources                                            | 21 |

| Pitfalls to Avoid                                              | 22 |

| Resources                                                      | 23 |

| Buck and LDO Power Mode Control                                | 23 |

| Load Switch Power Mode Control                                 | 24 |

| Dedicated Output Power Mode Control                            | 24 |

| Power Holdup Functionality (IN_PHUP)                           | 25 |

| Current Sense Amplifier                                        | 26 |

| Buck Regulators (BUCK1/2 - 2A Output)            | 26 |

|--------------------------------------------------|----|

| Setting Output Voltage                           | 26 |

| Output Monitoring                                | 26 |

| Enable and Power Mode Control                    | 27 |

| Active Discharge Resistor                        | 27 |

| Buck Regulators (BUCK3—3A Output)                | 28 |

| Setting Output Voltage                           | 28 |

| Active Discharge                                 | 28 |

| Output Monitoring                                | 28 |

| Enable and Power Mode Control                    | 29 |

| Load Switch Driver (LSW1/2)                      | 30 |

| Input Selection                                  | 30 |

| Output Drive                                     | 30 |

| Programming Soft-Start                           | 30 |

| Load Switch Controller Timing                    | 31 |

| Load Switch Driver (LSW3)                        | 32 |

| Input Selection                                  | 32 |

| Output Drive                                     | 32 |

| Programming Soft-Start                           | 32 |

| Linear Regulator                                 | 33 |

| Setting the Output Voltage                       | 33 |

| Active Discharge Resistor                        | 33 |

| Enable and Power Mode Control                    | 33 |

| I <sup>2</sup> C Serial Communications Interface | 34 |

| I <sup>2</sup> C Interface Power                 | 34 |

| I <sup>2</sup> C Acknowledge Bit                 | 34 |

| I <sup>2</sup> C Clock Stretching                | 34 |

| I <sup>2</sup> C General Call Address            | 34 |

| I <sup>2</sup> C Device ID                       | 34 |

| I <sup>2</sup> C Watchdog Timer                  | 34 |

| I <sup>2</sup> C Communication Speed       | 35 |

|--------------------------------------------|----|

| Write Protection                           | 35 |

| Writing to registers using the I2CWP bit   | 36 |

| I <sup>2</sup> C Communication Protocols   | 36 |

| Writing Multiple Bytes                     | 36 |

| Reading from a Single Register             | 36 |

| Reading from Sequential Registers          | 37 |

| I <sup>2</sup> C High-Speed Mode Extension |    |

| Register Descriptions                      | 38 |

| Global Resources                           | 39 |

| GLBL_INTO                                  | 39 |

| GLBL_INT1                                  | 40 |

| GLBLCNFG0                                  | 42 |

| GLBL_CNFG1                                 | 44 |

| GLBL_CNFG2                                 | 45 |

| GLBL_CNFG3                                 | 46 |

| GLBL_INTM                                  | 47 |

| HICCUP_CNFG                                | 48 |

| GLBL_STAT                                  | 49 |

| MSTRx_yFPS [x=0,1,2; y=x+3]                | 50 |

| BUCKxFPS [x=1,2,3]                         | 51 |

| LDOFPS                                     | 52 |

| LSWxFPS [x=1,2,3]                          | 53 |

| EREGxFPS [x=1,2]                           | 54 |

| OPMD1                                      | 55 |

| OPMD2                                      | 56 |

| CID0                                       | 57 |

| CID1                                       | 58 |

| CID2                                       | 59 |

| CID3                                       | 60 |

| CID4                                       | 61 |

| Current Sense Amplifier                    | 62 |

| CNFG_CSA                                         | 62 |

|--------------------------------------------------|----|

| Buck Regulators                                  | 63 |

| BUCK_INT                                         | 63 |

| BUCK_STAT                                        | 66 |

| BUCKxCNFG1 [x=1,2,3]                             | 67 |

| BUCKxCNFG2 [x=1,2,3]                             | 68 |

| BUCKxCNFG3 [x=1,2,3]                             | 70 |

| BUCKxCNFG4 [x=1,2,3]                             | 71 |

| BUCK3CNFG5                                       | 72 |

| Load Switch Drivers                              | 73 |

| LSW_INT                                          | 73 |

| CNFG_LSWx [x=1,2]                                | 74 |

| CNFG_LSW3                                        | 75 |

| Linear Regulator                                 | 76 |

| LDO_CNFG1                                        | 76 |

| I <sup>2</sup> C Serial Communications Interface | 77 |

| I2C_CTRL1                                        | 77 |

| I2C_CTRL2                                        | 78 |

| OTP Options                                      | 79 |

# List of Figures

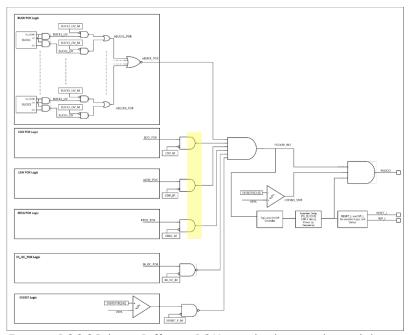

| Figure 1. PGOOD logic: Different POK signals, their masks, and the overall PGOOD signal                                                                           | 10 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

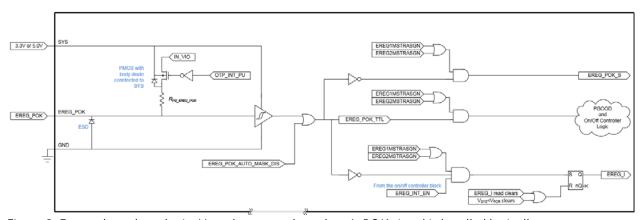

| Figure 2. External regulator logic: How the external regulator's POK signal is handled logically                                                                  | 14 |

| Figure 3. External regulator connections with External POK signals: Example of how to control external regulators' enables                                        |    |

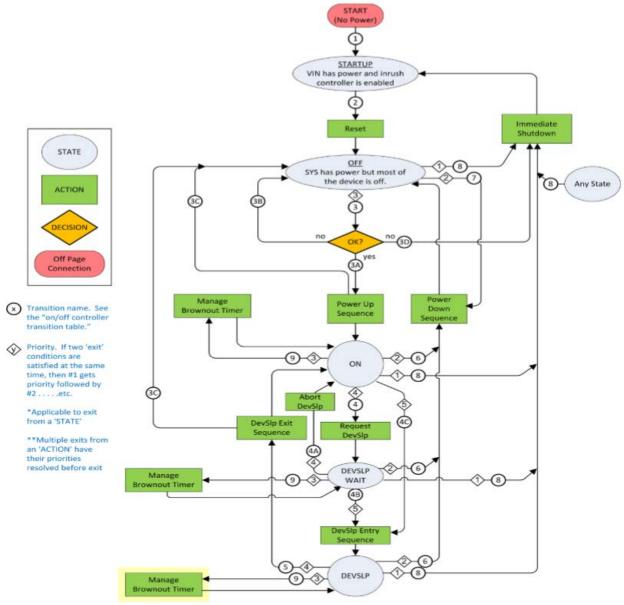

| Figure 4. On/Off controller flow: When the device shuts down and powers up                                                                                        | 15 |

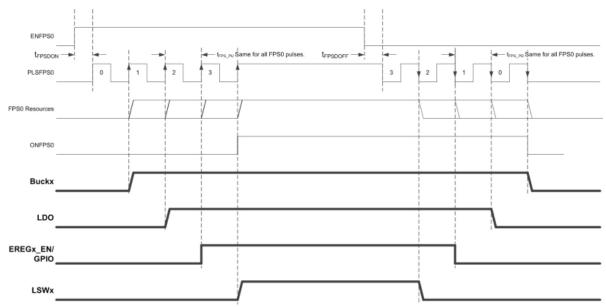

| Figure 5. Power-up and power-down sequencing example: How the power-down sequence is the reverse of the power-up sequence                                         | 20 |

| Figure 6. Flexible power sequencing—masters diagram: Visualization of the available number of FP masters and the number of slots provided by each pair of masters |    |

| Figure 7. Load switch start-up timing: Soft-start behavior of a load switch                                                                                       | 31 |

|                                                                                                                                                                   |    |

| List of Tables                                                                                                                                                    |    |

| Table 1: Reset Values Summary Table                                                                                                                               | 8  |

| Table 2: On/Off Controller Flow                                                                                                                                   | 16 |

| Table 3: Decode Logic for Buck and LDO Resources                                                                                                                  | 24 |

| Table 4: Decode Logic for Load Switch Resources                                                                                                                   | 24 |

| Table 5: Decode Logic for Dedicated Output Resource                                                                                                               | 25 |

| Table 6: Behavior of MAX77752 After Configuring HS_EXT                                                                                                            | 37 |

| Table 7: Reset Value Reference Table                                                                                                                              | 79 |

Maxim Integrated Page 6 of 83

# Overview

The MAX77752 provides multiple step-down regulators, flexible power sequencing, and external regulator enables in a compact package for applications where size is critical. While the data sheet for the device goes into detail describing the hardware and electrical characteristics of the device, this programmer's guide focuses on register descriptions and provides general advice for programmers.

Maxim Integrated Page 7 of 83

# **Reset Values**

The table below provides a quick summary of reset values based on the One-Time Programmable (OTP) version. See the table at the end of this document for a full list.

Table 1: Reset Values Summary Table

| Register                               | MAX77752A                                  | MAX77752B                                  |  |  |

|----------------------------------------|--------------------------------------------|--------------------------------------------|--|--|

| CID4                                   | 0x07                                       | 0x0D                                       |  |  |

| GLBL_CNFG1 Reset threshold = 2.65V     |                                            | Reset threshold = 2.85V                    |  |  |

| GLBL_CNFG2                             | Brownout threshold = 2.8V                  | Brownout threshold = 2.9V                  |  |  |

|                                        | Master mode                                | Slave mode                                 |  |  |

| OTP_PHUP_1                             | Enable pull-up resistors to all logic pins | Enable pull-up resistors to all logic pins |  |  |

| INRUSH_OPTION Inrush function selected |                                            | Inrush function selected                   |  |  |

| BUCK1CNFG1 Buck 1 Out = 1.8V           |                                            | Buck 1 Out = 1.8V                          |  |  |

| BUCK2CNFG1 Buck 2 Out = 1.350V         |                                            | Buck 2 Out = 1.200V                        |  |  |

| BUCK3CNFG1                             | Buck 3 Out = 1.05V                         | Buck 3 Out = 0.9V                          |  |  |

| LDOCNFG1                               | LDO Out = 1.800V                           | LDO Out = 1.875V                           |  |  |

Maxim Integrated Page 8 of 83

## Global Resources

# **Register Reset Conditions**

## SYS Undervoltage Lockout Comparator (SYSUVLO\_F\_I)

When  $V_{SYS}$  falls below  $V_{SYSUVLO}$ , SYSUVLO is asserted and the On/Off controller forces a system reset. The reset disables all functions of the power management integrated circuit (PMIC), shutting down the central bias and clocks. Check for this event with the SYSUVLO\_F\_I flag bit in the GLBL\_INT1 register.

#### System Reset Comparator (SYSRSTTH and SYSRSTHYS)

In addition to the fixed POR and undervoltage thresholds, there is a programmable system reset threshold, or VSYS\_RST, that generates an internal SYSGOOD signal. The threshold is programmable through SYSRSTTH[3:0] and hysteresis through SYSRSTHYS[1:0], both of which are in the GLBL\_CNFG1 register.

- SYSGOOD Assertion

- SYSGOOD is asserted when VSYS is above the rising VSYS\_RST threshold. This triggers the On/Off controller to trigger the power-up sequence.

- SYSGOOD De-Assertion

- When VSYS falls below the VSYS\_RST threshold, SYSGOOD is de-asserted, which triggers the On/Off controller to initiate a power-down sequence.

- The event is also recorded in the SYSRST\_F\_I flag in the GLBL\_INT1 register.

- In the GLBL\_INTM register, use the SYSRST\_F\_M bit to mask SYSRST\_F\_I in the GLBL\_INTO register and to mask the event itself from causing a power-down sequence. See the PGOOD Logic Diagram (Figure 1) for details.

#### System Brownout Comparator (SYSBO)

In the GLBL\_CNFG2 register, program the system brownout comparator with SYSBOTH[3:0] and its hysteresis with SYSBOHYS[1:0]. The brownout comparator's threshold is meant to be programmed higher than the SYS reset threshold. The SYS brownout comparator issues an early warning indication to the system controller of a falling supply voltage, so the system can react appropriately before power fails.

- SYSBO Assertion

- When the system voltage falls below the falling brownout threshold ( $V_{SYS} < V_{SYSBO (FALLING)}$ ), SYSBO is asserted. This causes the external PGOOD output to de-assert (LOW) immediately.

- If the brownout timer is enabled (setting the T\_BO\_EN bit in the GLBL\_CNFGO register), the system voltage is allowed a certain time period (tBO) to recover above the rising brownout threshold. If the timer expires and the system voltage has not recovered, the On/Off controller initiates a power-down sequence.

- If the brownout timer is disabled, no further action is taken in addition to the de-assertion of the PGOOD output.

- The event is also recorded by the SYSBO\_F\_I flag in the GLBL\_INT1 register.

Maxim Integrated Page 9 of 83

#### SYSBO De-Assertion

• When the system voltage rises above the rising threshold ( $V_{SYS} > V_{SYSBO (RISING)}$ ), SYSBO deasserts. This results in the external PGOOD output being allowed to assert (HIGH). Note that PGOOD is also controlled by other events. See the PGOOD Logic Diagram (Figure 1), for more details.

## Thermal Monitor (TOLVD)

TOVLD is recorded in the TOVLD\_I flag in the GLBL\_INT1 register.

### Chip Identification (CID)

The chip identification feature allows software to recognize different revisions of the MAX77752. When contacting Maxim for assistance with a given device, you might be asked for the values of the CID registers. Note that the serial number contained in CID0, CID1, and CID2 might not be unique for each device; however, the serial number, purchase order, top mark, and date code can improve Maxim's ability to provide customer support.

## PGOOD Output (PG\_DLY)

- During a power-up sequence, PGOOD is asserted once the power up sequence is complete and the internal PGOOD signal (PGOOD\_INT which denotes the POK status of all regulators as well as the system voltage) is asserted. There is an assertion delay programmed by PG\_DLY[1:0] in the GLBL\_CNFG3 register. Refer to the power-up sequence example timing diagram (Figure 5) for details.

- PGOOD is always left asserted including in the DevSlp state.

- PGOOD can de-assert at any time if a regulator's undervoltage (UV), overvoltage(OV), or overcurrent (OC) (overcurrent only for Bucks) status signals assert and they are unmasked. Refer to the PGOOD Logic Diagram (Figure 1) below for complete details.

Figure 1. PGOOD logic: Different POK signals, their masks, and the overall PGOOD signal.

Maxim Integrated Page 10 of 83

# Low Power (OTP\_PHUP\_1)

This device supports Low Power mode and DevSlp mode, to further reduce power consumption when the system itself is entering a sleep state. Low Power mode implies the regulators' (BUCK1, BUCK2, BUCK3, etc.) behavior in low power; DevSlp mode implies the On/Off controller's behavior in low power. Depending on the OTP option, certain rails can be powered down and Buck 3 might transition to its Low Power mode voltage. Controllers can use three pins depending on whether the PMIC is configured to be in Master mode or Slave mode.

If this device is in Master mode, the application uses the LP\_MODE, LP\_REQ, and LP\_ACK pins. Otherwise, if the device is in Slave mode, only LP\_ACK is used.

The OTP\_SLP\_MSTR\_SLV bit in the OTP\_PHUP\_1 register configures the mode as follows:

- 0—Master mode

- 1—Slave mode

See the Reset Value Reference Table (Table 7) at the end of this document to determine whether your device is in Master mode or Slave mode.

#### LP\_MODE Input

If this device is in Slave mode, then the LP\_MODE input is a "don't care" and can be left unconnected or tied high or low.

LP\_MODE is the pin that the controller uses to make a Low Power mode request to the MAX77752. After the controller requests Low Power mode, this device sends the same request to other devices it is powering with the LP\_REQ pin. The other devices respond to the MAX77752 through the LP\_ACK pin.

- LP\_MODE is a push-pull input.

- LP\_MODE is referenced to the IN\_VIO to set its logic high and low thresholds.

- LP\_MODE is debounced and sent to the On/Off controller to request entry into DevSlp mode.

- Set this pin high to request this device to enter DevSlp mode.

- Setting LP\_MODE low while this device is waiting for acknowledgement (LP\_ACK) from other devices aborts entry into DevSIp mode and returns the device to the On state.

- Setting LP\_MODE low while the device is already in DevSlp mode triggers the On/Off controller to exit DevSlp mode. It also triggers the LP\_REQ de-assertion timer to start.

## LP\_REQ Output (OTP\_INT\_PU and ALT\_LP\_REQ)

LP\_REQ is an open-drain output that this device uses to send a Low Power mode request signal to other devices it is powering. Those devices can then acknowledge the request through the LP\_ACK pin. See the description above of the LP\_MODE pin to learn when the LP\_REQ pin is asserted.

In an example application in which one or more rails power down in Low Power mode or DevSlp mode, this device might send a Low Power mode request to a system, letting the system know to finish its tasks or shut down anything it is controlling. Then the system acknowledges this device, letting the PMIC know that the system is ready for power to be removed.

- LP\_REQ is an active-high output with an optional internal  $100k\Omega$  pull-up resistor to IN\_VIO. The OTP\_INT\_PU bit in the OTP\_PHUP\_1 register determines if the internal resistor is used.

- LP\_REQ is relevant when the PMIC is configured in Master mode (OTP\_SLP\_MSTRSLV = 0).

Maxim Integrated Page 11 of 83

- If the PMIC is configured to be in the Slave mode (OTP\_SLP\_MSTRSLV = 1), then LP\_REQ is kept de-asserted, or logic low. Not populating an external pull-up resistor is acceptable in this case.

- The ALT\_LP\_REQ\_EN bit configures LP\_REQ to work in an I<sup>2</sup>C controlled alternate mode in Slave mode. The logic level during this mode can be set high by ALT\_LP\_REQ = 1. Both the ALT\_LP\_REQ\_EN and ALT\_LP\_REQ flags are in the GLBL\_CNFGO register.

#### LP\_ACK Input (OTP\_LPACK\_POL)

LP\_ACK is a push-pull input from a controller to the MAX77752 representing the Low Power mode acknowledge. In Master mode, the acknowledge is a response caused by assertion of the LP\_REQ output. Otherwise, in Slave mode, the signal triggers the PMIC to immediately go into Low Power mode, or DevSlp mode.

- LP\_ACK is an active-high input with an optional, internal  $100k\Omega$  pull-up resistor to VIO (OTP\_INT\_PU = 1).

- LP\_ACK is configured to be active low or high by the OTP\_LPACK\_POL bit in the SPARE\_OTP register.

- OTP\_LPACK\_POL = 0 configures LP\_ACK as active high.

- OTP\_LPACK\_POL = 1 configures LP\_ACK as active low.

- When configured in Master mode (OTP\_SLP\_MSTRSLV = 0), the PMIC asserts LP\_REQ upon a LP\_MODE assertion and waits for a LP\_ACK assertion indefinitely. This is the DevSlp Wait state. Once a LP\_ACK assertion is received, the PMIC goes into DevSlp mode.

- When configured in Slave mode (OTP\_SLP\_MSTRSLV = 1), the PMIC remains in the ON state until an LP\_ACK is asserted by a controller.

## WP\_L Output

WP\_L is an open-drain output to the memory in the system that represents a write-protect function.

- WP\_L is an active-low output with an optional, internal  $100k\Omega$  pull-up resistor to VIO (OTP\_INT\_PU = 1).

- During the power-up sequence (see the figures and timing diagrams in the On/Off Controller section), WP\_L is asserted after the RESET\_L output assertion.

- There is a WP\_L de-assertion delay programmed by WP\_L\_DLY[1:0] in the GLBL\_CNFG3 register that is started when the RESET\_L output is asserted.

- During the power-down sequence, WP\_L is asserted without any delay along with the PGOOD and RESET\_L outputs.

- When the PMIC is configured in Master mode or Slave mode (OTP\_SLP\_MSTRSLV = 0 or 1), WP\_L is asserted without any delay along with RESET\_L outputs.

- While exiting from DevSlp state, WP\_L is de-asserted after the power-up sequence is complete. The de-assertion delay is programmed by WP\_L\_DLY[1:0].

#### External Regulator Enable/Disable Control

The PMIC has three I/O pins: EREG\_EN1, EREG\_EN2, and EREG\_POK. These are intended to enable two external regulators and process their power okay (POK) signals. If the POK signals indicate an issue, the

Maxim Integrated Page 12 of 83

PMIC transitions to the Off state and sets an internal flag (EREG\_I) in the BLGL\_INTO register, indicating that an issue occurred.

## External Regulator Enable/Disable Outputs (EREG\_EN1, EREG\_EN2)

- See the Register Descriptions section at the end of this document for additional details on the bit descriptions.

- EREG EN1 and EREG EN2 can be operated independently in one of two modes:

- Control EREG\_ENx manually by clearing the master assign bit (EREGxMSTRASGN = 0) from the EREGxFPS registers and then control the logic level with EREGxOPMD flags from the OPMD2 register.

- Set the master assign bit (EREGxMSTRASGN = 1) to allow the flexible power sequencer to automatically control EREG\_ENx

- o Choose active-high or active low (EREGxOPMD)

- o Program the desired master (EREGxMSTR[2:0])

- o Choose the power-up slot (EREGxUPSLT[1:0])

- o Choose the power down slot (EREGxDNSLT[1:0])

- During the On state, if EREG\_POK is pulled low by an EREG\_ENx pin, which is assigned to an FPS Master (EREGxMSTRASGN = 1), a power-down event is initiated.

- EREG\_POK is pulled low when transitioning from the On state to DevSlp and back to the On state if any of the EREG\_ENx resources on the FPS Master (EREGxMSTRASGN = 1) is disabled.

Use the OTP\_EREG\_POK\_AUTO\_MASK\_DIS bit in the SPARE\_OTP register to choose the behavior of the PMIC.

- OTP\_EREG\_POK\_AUTO\_MASK\_DIS = 0: EREG\_POK pin output is internally masked and power-down event does NOT initiate

- OTP\_EREG\_POK\_AUTO\_MASK\_DIS = 1: EREG\_POK pin output is not masked and powerdown event initiates

- EREG\_ENx has optional internal pull-up resistors:

- When OTP INT PU = 1, EREG ENx is internally pulled up through RPU EREG POK.

- When OTP\_INT\_PU = 0, EREG\_ENx is not internally pulled up.

- Output Drive Capability:

- $\bullet$  When the pin voltage is driven greater than  $V_{SYS}$ , set the ALT\_EREG2EN\_EN bit in the GLBL\_CNFG1 register to avoid internal leakage path.

# EREG\_POK Input

- The functional logic for EREG\_POK is shown in the figure below (Figure 2). See the Register Descriptions section for additional details on the bit descriptions.

- EREG\_POK has an optional internal pull-up resistor configurable with the OTP\_INT\_PU flag in the OTP\_PHUP\_1 register.

Maxim Integrated Page 13 of 83

- When OTP\_INT\_PU = 1, EREG\_POK is internally pulled up to IN\_VIO through RPU\_EREG\_POK.

- When OTP\_INT\_PU = 0, EREG\_POK is not internally pulled up.

- EREG\_POK is capable of affecting the PGOOD and On/Off controller logic.

- When EREG\_M = 0 in the GLBL\_INTM register, EREG\_POK being low causes PGOOD\_INT to be low.

- EREG\_POK is allowed to affect the PGOOD and On/Off controller logic when it is unmasked (EREG\_M = 0). Any EREG\_ENx outputs controlled by the flexible power sequencer (EREG1MSTRASGN OR EREG2MSTRASGN = 1) and EREG\_POK go low while the On/Off controller logic enables the POK interrupt (EREG\_INT\_EN = 1). If EREG\_I is driven high to the PGOOD and On/Off control logic, PGOOD goes low and the On/Off controller transitions to the Off state.

- If the EREG\_POK input is not required for a given application:

- Leave EREG\_POK unconnected if the device has the internal pull-up resistor enabled (OTP\_INT\_PU = 1).

- Connect EREG\_POK to SYS if the device has the internal pull-up resistor disabled (OTP INT PU = 0).

Figure 2. External regulator logic: How the external regulator's POK signal is handled logically.

Use Case—Two external regulators in the system that are both being driven by the flexible power sequencer:

- Set the EREG1MSTRASGN and EREG2MSTRASGN bits to place both regulators on the flexible power sequencer output.

- If EREG\_POK is logic high when the On/Off controller sets EREG\_POK\_EN = 1, everything is okay with the external regulators and the system operates normally.

- If EREG\_POK ever goes low while the On/Off controller has EREG\_POK\_EN = 1, the external regulators have a problem, and the On/Off controller transitions to the OFF state. The EREG\_I flag is set internally, so software can learn that there was an external regulator issue on the subsequent power up.

Maxim Integrated Page 14 of 83

Figure 3. External regulator connections with External POK signals: Example of how to control external regulators' enables.

# On/Off Controller

The following diagram is a top-level description of a flow for an On/Off controller that is controlling the state of the PMIC and, consequently, the individual regulators.

Figure 4. On/Off controller flow: When the device shuts down and powers up.

The following table lists the detailed transition conditions for the On/Off controller flow.

Maxim Integrated Page 15 of 83

Table 2: On/Off Controller Flow

| Transition | Condition                                                                                                                                 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | Input voltage to the system is above V <sub>in</sub> UVLO threshold (sensed by VIN_SNS).                                                  |

| 1          | $V_{IN} > V_{IN\_UVLO}$                                                                                                                   |

|            | The fundamental system voltages and resources are available. Move to the OFF state.                                                       |

|            | The system voltage (V <sub>SYS</sub> ) is not undervoltage.                                                                               |

| 2          | SYSUVLO = 0                                                                                                                               |

|            | The inrush controller has completed soft-start.                                                                                           |

|            | IN_SS_DONE = 1                                                                                                                            |

|            | A wake-up signal has been received. Move to the "OK?" state to check if the system is okay to wake up.                                    |

|            | V <sub>SYS</sub> > V <sub>SYS_RESET</sub> (rising threshold) threshold.                                                                   |

|            | SYSGOOD = 1                                                                                                                               |

| 2          | The Disable Wake Up bit is 0. DISWK = 0                                                                                                   |

| 3          |                                                                                                                                           |

|            | See the GLBL_CNFGO register in the Register Descriptions section for more details.  Hiccup counter is less than the hiccup counter limit. |

|            | HICCUP_CNT < HICCUP_CNT_LIM                                                                                                               |

|            | See the HICCUP_CNFG register in the Register Descriptions section for more details.                                                       |

|            | The basic system resources are okay.                                                                                                      |

|            | The system voltage is above the required threshold.                                                                                       |

| 3A         | SYSGOOD = 1                                                                                                                               |

|            | The junction temperature is below the temperature overload threshold.                                                                     |

|            | TOVLD = 0                                                                                                                                 |

| 3B         | Failed attempt to power up because the system voltage was below the required threshold.                                                   |

| 30         | SYSGOOD = 0                                                                                                                               |

|            | Failed attempt to power up successfully. At least one of the regulators in the power-up sequence did not                                  |

| 3C         | assert its POWERGOOD (POK) output before the Power Good period expired.                                                                   |

|            | TPGOOD_EXP = 1 and PGOOD = 0                                                                                                              |

|            | Failed attempt to power up because the junction temperature was too high, or the system voltage was too                                   |

| 3D         | high.                                                                                                                                     |

|            | TOVLD = 1                                                                                                                                 |

|            | Enter DevSlp Wait state.                                                                                                                  |

| 4          | The PMIC is in Master mode (See the OTP_PHUP_1 register in the Register Description section) OTP_SLP_MSTRSLV = 0                          |

| 4          | LP_MODE (de-bounced) is high.                                                                                                             |

|            | LP_MODE_DEB = 1                                                                                                                           |

|            | Abort DevSlp entry.                                                                                                                       |

|            | The PMIC is in Master mode                                                                                                                |

| 4A         | OTP_SLP_MSTRSLV = 0                                                                                                                       |

|            | LP_MODE (de-bounced) is low.                                                                                                              |

|            | LP_MODE_DEB = 0                                                                                                                           |

|            | Enter DevSlp Wait state (Master mode).                                                                                                    |

|            | The PMIC is in Master mode.                                                                                                               |

| 4B         | OTP_SLP_MSTRSLV = 0                                                                                                                       |

| .5         | LP_MODE (de-bounced) remained high from 4A.                                                                                               |

|            | There is a rising edge on LP_ACK.                                                                                                         |

|            | LP_ACK = 0→1                                                                                                                              |

|            | Enter DevSlp State (Slave mode).                                                                                                          |

| 40         | The PMIC is in Slave mode.                                                                                                                |

| 4C         | OTP_SLP_MSTR_SLV = 1 There is a rising edge on LP_ACK.                                                                                    |

|            | There is a rising edge on LP_ACK. $LP_ACK = 0 \rightarrow 1$                                                                              |

|            | E _7/6/( = 0.7)                                                                                                                           |

Maxim Integrated Page 16 of 83

|   | Exit DevSlp mode.                                                                                        |

|---|----------------------------------------------------------------------------------------------------------|

| 5 | The PMIC is in Master mode and LP_MODE is low.                                                           |

|   | OTP_SLP_MSTRSLV = 0                                                                                      |

|   | LP MODE = 0                                                                                              |

|   | Or the PMIC is in slave mode and LP_ACK is low.                                                          |

|   | OTP_SLP_MSTRSLV = 1                                                                                      |

|   | LP_ACK=0                                                                                                 |

|   | Enter the Power-Down sequence.                                                                           |

| 6 | This state is initiated when "Start_Power_Down = True" in the pseudo code shown below in the Hiccup      |

|   | Count Algorithm section.                                                                                 |

|   | Enter the Power-Down sequence from the Off state.                                                        |

| 7 | Software Power Off.                                                                                      |

| / | SFT_OFF_NORST = 1 OR SFT_OFF_SYSRST = 1                                                                  |

|   | See the GLBL_CNFGO register in the Register Description section for more details.                        |

|   | Move to the Immediate Shutdown state.                                                                    |

|   | The junction temperature is too high.                                                                    |

|   | TOVLD_I = 1                                                                                              |

| 8 | The system voltage is low.                                                                               |

|   | SYSUVLO_I = 1                                                                                            |

|   | Bias is not stable.                                                                                      |

|   | BRDY_I = 0                                                                                               |

|   | Manage Brownout Timer.                                                                                   |

|   | System voltage has dropped below brownout threshold and brownout timer is enabled.                       |

|   | Vsys < Vsys_Bo (Falling)                                                                                 |

| 9 | T_BO_EN = 1                                                                                              |

|   | See the GLBL_CNFGO register in the Register Description section for more details.                        |

|   | System voltage has risen above brownout threshold, brownout timer is enabled, and brownout timer has not |

|   | expired.                                                                                                 |

|   | V <sub>SYS</sub> > V <sub>SYS_BO</sub> (Rising)                                                          |

|   | T_BO_EN = 1                                                                                              |

|   | BO_TMR_EXP = 0                                                                                           |

Maxim Integrated Page 17 of 83

### Hiccup Count Algorithm

```

for buck in [BUCK1, BUCK2, BUCK3]:

if \ BUCK\_M == 0 \& SS\_DONE\_buck == 1 \& ((UV\_buck == 1 \& buck\_UV\_M == 0) | (OV\_buck == 1 \& buck\_OV\_M == 0)) : \\

HICCUP_CNT+=1

PGOOD=0

Start_Power_Down = True

for Isw in [LSW1, LSW2, LSW3]:

if lsw_M==0 \& SS_DONE_lsw==1 \& (UV_lsw==1 \& lsw_UV_M==0):

HICCUP_CNT+=1

PGOOD=0

Start Power Down = True

if LDO_M==0 & SS_DONE_LDO==1 & (UV_LDO==1 & LDO_UV_M==0):

HICCUP CNT+=1

PGOOD=0

Start_Power_Down = True

if EREG_M==0 & t_PG_DLY==DONE & EREG_POK==0:

HICCUP CNT+=1

PGOOD=0

Start_Power_Down = True

if IN_OC_M==0 & t_PG_DLY==DONE & IN_OC==1:

HICCUP_CNT+=1

PGOOD=0

Start_Power_Down = True

if T_BO_EN==1 & BO_TMR_EXP==1 & SYS_BO==1 & PG_DLY==DONE:

HICCUP_CNT+=1

PGOOD=0

Start_Power_Down = True

if SYSRST_F_M=0 & SYS_RST==1:

# the design intentionally excludes incrementing the hiccup counter here

PGOOD=0

Start_Power_Down = True

if IN_OVLO==1:

# the design intentionally excludes incrementing the hiccup counter here

PGOOD=0

Disable_Inrush = True

if SFT_OFF_NORST==1:

Start_Power_Down = True

if SFT_OFF_SYSRST==1:

Start_Power_Down = True

```

## Flexible Power Sequencer

The Flexible Power Sequencer (FPS) allows resources to power up under hardware or software control. Additionally, each resource can power up independently or among a group of other regulators with an adjustable power-up and power-down delays (sequencing). However, if there is an event that initiates immediate shutdown (e.g., input undervoltage) the device does not go through sequenced power-down. See the On/Off Controller Flow diagram (Figure 4) for more details on when the sequencing occurs.

Maxim Integrated Page 18 of 83

The flexible sequencing structure consists of six master sequencing timers and nine resources. Each master sequencing timer is programmable through its configuration register (MSTRx\_yFPS). When enabled/disabled, a master sequencing timer generates four sequencing slots. The time between each slot is programmable within the FPS register, as described below.

The signals to turn on a resource rise at the end of a slot duration. For example, if master 0's (FPS0) slot duration is programmed to  $31\mu$ s and master 1's (FPS1) slot duration is programmed to  $63\mu$ s, the power up sequence is as follows:

- 1. The power-up sequence starts.

- 2. 31µs pass

- 3. FPSO Slot 0 resources power on.

- 4. 31μs pass

- 5. FPSO Slot 1 resources power on.

- 6. 31μs pass

- 7. FPSO Slot 2 resources power on.

- 8. 31µs pass

- 9. FPSO Slot 3 resources power on.

- 10. 63µs pass

- 11. FPS1 Slot 0 resources power on.

- 12. 63µs pass

- 13. FPS1 Slot 1 resources power on.

- 14. Etc.

Nine resources within the MAX77752 have centrally based flexible power sequence enable/disable capabilities. With the MSTRASGN bits in the [Buckx, LDO, LSWx, EREGx]FPS registers, specify any of these nine resources to be enabled/disabled by the flexible power sequencer.

The figure below shows an example of four resources powering up under the control of flexible power sequencer 0.

Maxim Integrated Page 19 of 83

Figure 5. Power-up and power-down sequencing example: How the power-down sequence is the reverse of the power-up sequence.

#### Masters

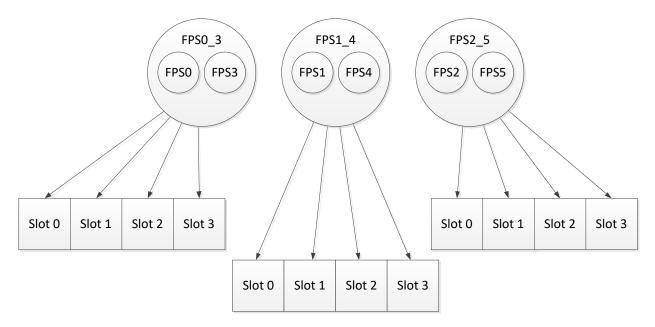

There are six masters from FPSO to FPS5 that control the power-up and power-down sequence of resources. These masters are also paired, e.g., masters FPSO and FPS3 are paired as FPSO\_3. See Figure 6 for a visualization.

- FPSO, FPS1, and FPS2 power down during the entry to DevSlp State and power up again when exiting from DevSlp back to the ON state.

- The pairs of masters are: FPSO\_3, FPS1\_4, and FPS2\_5.

- Each pair of masters provides four sequencing slots.

- When enabled, a total of 12 slots (three pairs with four slots each) allows a sequenced power up.

- Each pair of masters powers on or down sequentially—that is, master 0 and master 3 power on or down in parallel, then master 1 and master 4, and then master 2 and master 5.

- Each pair of masters has independently programmable power-up and power-down slot durations using the MSTRx\_y FPS registers, where x = 0, 1, 2, and y = x + 3.

- Power-up and power-down slots are programmable through register bits MSTRx\_yUPF[2:0] and register bits MSTRx\_yDNF[2:0], respectively.

- Power-up and power-down slot duration range is from 30μs to 3906μs in eight binary weighted steps.

Maxim Integrated Page 20 of 83

Figure 6. Flexible power sequencing—masters diagram: Visualization of the available number of FPS masters and the number of slots provided by each pair of masters.

#### Available Resources

The device contains the following resources that can be part of the flexible power sequencer with the following programmable options:

- 3x buck converters through the BUCKxFPS registers

- Independently programmable power-down slot number within the master through BUCKxDNSLT[1:0]

- Independently programmable power-up slot number within the master through BUCKxUPSLT[1:0]

- Independently programmable master assignment for power-up AND power-down through BUCKxMSTR[2:0]

- Independently programmable ability to be part of a master or not through BUCKxMSTRASGN

- 1x low dropout (LDO) linear regulator through the LDOFPS register

- Independently programmable power-down slot number within the master through LDO\_DNSLT[1:0]

- Independently programmable power-up slot number within the master through LDO\_UPSLT[1:0]

- Independently programmable master assignment for power up AND power down through LDO\_MSTR[2:0]

- Independently programmable ability to be part of a master or not through LDO\_MSTRASGN

- 3x load switch controllers through the LSWxFPS registers

Maxim Integrated Page 21 of 83

- Independently programmable power-down slot number within the master through LSWxDNSLT[1:0]

- Independently programmable power-up slot number within the master through LSWxUPSLT[1:0]

- Independently programmable master assignment for power up AND power down through LSWxMSTR[2:0]

- Independently programmable ability to be part of a master or not through LSWxMSTRASGN

- 2x dedicated (external regulator control) through the EREGxFPS registers

- Independently programmable power-down slot number within the master through EREGxDNSLT[1:0]

- Independently programmable power-up slot number within the master through EREGxUPSLT[1:0]

- Independently programmable master assignment for power-up AND power-down through EREGxMSTR[2:0]

- Independently programmable ability to be part of a master or not through EREGxMSTRASGN

#### Pitfalls to Avoid

The flexible power sequencer provides for a tremendous amount of configurability and flexibility. However, this comes at the risk of unforeseen situations in a system. Here are some guidelines to avoid such risks:

- Because internal regulator POK signals are masked to be high (i.e., power is OK) while they are soft-starting, the PGOOD output asserts high immediately for a regulator configured to power up in the last slot (i.e., Slot 3 of FPS2 or FPS5). This is observable as a rising edge on the PGOOD output before the regulator in the last slot has completed its soft-start and reached its valid output voltage.

- o If the desired power-up sequence requires a regulator in the last power-up slot as described above, program the PGOOD assertion delay through PG\_DLY[1:0] in the GLBL\_CNFG3 register to insert a delay between the regulator soft-start and the PGOOD assertion.

- If a regulator's output is the input for another regulator, configure the first to be enabled early enough in the sequence, so it has completed its soft-start before the other regulator is enabled.

- If a regulated output from the MAX77752 serves as a pull-up supply for a signal on an external regulator in the system, Maxim recommends configuring the sequence such that the internal regulator is enabled first, before the external regulator.

- o Ex: LSW2 is a pull-up voltage for an external regulator's POK output. Enable LSW2 before the external regulator and disable it after the external regulator.

- Enable the regulator that supplies the VIO pin at least 2µs after the supply at VIO has reached the nominal level and before executing any I<sup>2</sup>C commands.

Maxim Integrated Page 22 of 83

o Ex: If LSW1 supplies VIO, avoid configuring LSW1 on slot 3 of FPS2 for FPS5 masters during a power-up sequence or DevSlp exit sequence. Even if this is done, ensure that LSW1 soft-start is complete at least 2µs before RESET\_L de-assert.

#### Resources

The above-mentioned slave resources are grouped by common characteristics and configuration. Each resource type has different I/O signals to control the resource, depending on the usage, power state and special cases. The resources are as follows:

- Buck resource through the OPMD1 register

- Output Signal—Controls buck regulator enable/disable through register bits BUCKxOPMD[1:0]

- Output Signal—Controls Low Power mode (LPM) enable/disable signals

- Input Signal—Power Good/VOK from buck regulator

- LDO resource through the OPMD2 register

- Output Signal—Controls linear regulator enable/disable through register bits LDOOPMD[1:0]

- Output Signal—Controls Low Power mode (LPM) enable/disable signals

- Input Signal—Power Good/VOK from linear regulator

- Load switch resource

- Output Signal—Controls load switch enable/disable through register bit LSWxOPMD through external pin

- Input Signal—Power Good/VOK from load switch; through external pin

- External Regulator Resource through the OPMD2 register

- Output Signal—Controls external regulator enable/disable through register bit EREGxOPMD; through external pin

- Input Signal—Power Good/VOK from external regulator; through external pin

#### Buck and LDO Power Mode Control

The following table enumerates the various possible modes that the buck converter or LDO linear regulator can be placed in based on the sequencer configuration and the individual buck/LDO power mode configurations. Do NOT change the BUCKxMSTRASGN/LDOMSTRASGN bit while the regulator is already enabled in the ON state, because this can cause a glitch on the regulator output.

Maxim Integrated Page 23 of 83

Table 3: Decode Logic for Buck and LDO Resources

| #  | Register Bit                   | Internal | Signal      | Register Bit     | Register Bit | Internal Signal | Inter                      | nal Signal      |                             |

|----|--------------------------------|----------|-------------|------------------|--------------|-----------------|----------------------------|-----------------|-----------------------------|

| 0  | BUCKxMSTRASGN /<br>LDOMSTRASGN |          | DEVSLP_FLAG | DUIOU ODNIDIAL / |              |                 | BUCKx_LPMEN /<br>LDO_LPMEN | BUCK3DVS_DEVSLP | Mode                        |

| 1  | 0                              | х        | х           | 0                | 0            | 0               | 0                          | 0               | OFF                         |

| 2  | 0                              | ×        | 0           | 0                | 1            | 1               | 0                          | 0               | Enabled,<br>Normal<br>Power |

| 3  | 0                              | х        | 1           | 0                | 1            | 1               | 1                          | Based on OTP    | Enabled,<br>Low Power       |

| 4  | 0                              | x        | x           | 1                | 0            | 1               | 1                          | 0               | Enabled,<br>Low Power       |

| 5  | 0                              | х        | х           | 1                | 1            | 1               | 0                          | 0               | Enabled,<br>Normal<br>Power |

| 6  | 1                              | 0        | х           | х                | х            | 0               | 0                          | 0               | OFF                         |

| 7  | 1                              | 1        | х           | 0                | 0            | 1               | 0                          | 0               | OFF                         |

| 8  | 1                              | 1        | 0           | 0                | 1            | 1               | 0                          | 0               | Enabled,<br>Normal<br>Power |

| 9  | 1                              | 1        | 0           | 0                | 1            | 1               | 1                          | Based on OTP    | Enabled,<br>Low Power       |

| 10 | 1                              | 1        | 1           | 1                | 0            | 1               | 1                          | 0               | Enabled,<br>Low Power       |

| 11 | 1                              | 1        | 1           | 1                | 1            | 1               | 0                          | 0               | Enabled,<br>Normal<br>Power |

#### Load Switch Power Mode Control

The following table enumerates the various possible modes that the load switch can be placed in based on the sequencer configuration and the individual load switch power mode configurations. Do NOT change the LSWxMSTRASGN bit while the regulator is already enabled in the ON state, because this can cause a glitch on the load switch output.

Table 4: Decode Logic for Load Switch Resources

| # | Register Bit | Internal Signal | Register Bit | Internal Signal |      |

|---|--------------|-----------------|--------------|-----------------|------|

| 0 | LSWxMSTRASGN | FPS_EN_LSWx     | LSWxOPMD[0]  | LSWx_EN         | Mode |

| 1 | 0            | х               | 0            | 0               | OFF  |

| 2 | 0            | х               | 1            | 1               | ON   |

| 3 | 1            | 0               | х            | 0               | OFF  |

| 4 | 1            | 1               | х            | 1               | ON   |

## Dedicated Output Power Mode Control

The following table enumerates the various possible modes that dedicated output (EREG\_ENx) can be placed in through the configuration in the flexible power sequencer.

Do NOT change the EREGxMSTRASGN bit while in the ON state, because this can cause a glitch on the EREG\_ENx output.

Maxim Integrated Page 24 of 83

Table 5: Decode Logic for Dedicated Output Resource

| # | Register Bit  | Internal Signal | Register Bit | Internal Signal |                    |

|---|---------------|-----------------|--------------|-----------------|--------------------|

| 0 | EREGxMSTRASGN | FPS_EN_EREGx    | EREGxOPMD    | EREG_Enx        | EREGx Logic State  |

| 1 | 0             | х               | 0            | 0               | LOW                |

| 2 | 0             | х               | 1            | 1               | HIGH               |

| 3 | 1             | 0               | 0            | 0               | LOW (Active High)  |

| 4 | 1             | 1               | 0            | 1               | HIGH (Active High) |

| 5 | 1             | 0               | 1            | 1               | HIGH (Active Low)  |

| 6 | 1             | 1               | 1            | 0               | LOW (Active Low)   |

# Power Holdup Functionality (IN\_PHUP)

IN\_PHUP is an analog power input pin. This pin is connected to the output of the power holdup IC. This pin provides power to a selected internal block that maintains the logic level of EREG\_EN1, WP\_L, and PGOOD (internal) during a SYS power fail event. The power holdup flow can be accessed in the On/Off Controller section. If this function should be disabled, the OTP\_PHUP\_EN flag in the OTP\_PHUP\_1 register must be cleared.

In case of a fault condition in which the HICCUP\_CNT\_EXPIRE = 1 in the HICCUP\_CNFG register, this pin can be used to provide power to the  $I^2C$  block.

Maxim Integrated Page 25 of 83

# **Current Sense Amplifier**

The current sense amplifier (CSA) circuit monitors the input current into the system by comparing against a set threshold. If the input current exceeds the threshold for more than the debounce timer period, an interrupt is generated,  $IN\_OC\_I = 1$  in the GLBL\_INTO register, and a power-down event initiates if  $IN\_OC\_M = 0$  in the GLBL\_INTM register. Configure OTP\_CSA\_DBNC in the SPARE\_OTP register to set the debounce timer period to  $50\mu s$  or  $100\mu s$ . The default is  $100\mu s$ . Two register bits (CSTH\_OTP[1:0] in the CNFG\_CSA register) are available to set the current threshold, the default is 45mV (2.25A), and a  $R_{SENSE}$  resistor of  $20m\Omega$  ±1% is recommended for the application.

# Buck Regulators (BUCK1/2 - 2A Output)

BUCK1 and BUCK2 are step-down converters with the following:

- Programmable output voltage from 0.600V to 2.194V in 6.25mV steps

- Programmable brownout and overvoltage comparators

# Setting Output Voltage

Set the output voltage with BUCKxVOUT[7:0] in the BUCKxCNFG1 register, where each step is 6.25mV. For example, to set BUCK1 to output 1.2V, BUCK1CNFG1 = 0x53.

# **Output Monitoring**

BUCK1 and BUCK2 have multiple ways of ensuring the health of their output.

- There is a programmable brownout monitor that sets an interrupt flag (BUCKx\_UV\_I) in the BUCK\_INT register when the output voltage falls below the programmed brownout threshold.

- To have the brownout on the output of the buck initiate a power-down sequence, clear the BUCKx\_UV\_M bit in the BUCK\_INTM register.

- When the buck is first enabled, either through I<sup>2</sup>C or by the sequencer, the buck control circuit attempts to ramp the output voltage as fast as possible to the target output (programmed by BUCKxVOUT[7:0] in the BUCKxCNFG1 register) limited only by the PMOS peak current limit. During this process of output voltage ramp, the brownout output is prevented from being triggered until the end of the soft-start period (determined by the specified ramp-up slew rate).

- However, if the output capacitance is large enough, the soft-start process completes before the output reaches the rising UV threshold and thereby the UV interrupt sets, although the output would eventually rise above the UV threshold.

- When the output voltage for BUCK1 or BUCK2 is decreased through I<sup>2</sup>C after they have been enabled, the buck control circuit changes the output voltage target directly to the final value. In such a case, the brownout comparator naturally provides an undervoltage assertion, which if not masked by BUCKx\_UV\_M, causes a power-down sequence. If such a use case is foreseen, set the mask bits first and then change the output voltage. Alternatively, the change in output voltage should be done in small steps. Note that even if the mask bit is set, the corresponding interrupt bit is still set.

- Note that a load transient on the output of the buck at a fast slew rate and a large magnitude has the capability to cause an output voltage droop that causes the UV comparator to trip and flag an undervoltage event, if the brownout threshold is set high (such as 90%).

Maxim Integrated Page 26 of 83

- There is a programmable overvoltage monitor that sets an interrupt flag (BUCKx\_OV\_I) when the output voltage rises above the programmed overvoltage threshold.

- To allow the overvoltage on the output of the buck to initiate a power-down sequence, clear the BUCKx\_OV\_M bit.

- When the buck is first enabled, either through I<sup>2</sup>C or by the sequencer, the buck control circuit attempts to ramp the output voltage as fast as possible to the target output (programmed by BUCKxVOUT[7:0]), limited only by the PMOS peak current limit. During this process of output voltage ramp, the overvoltage output is prevented from triggering until the end of the soft-start period (determined by the specified ramp-up slew rate).

- When the output voltage for BUCK1 or BUCK2 is increased through I<sup>2</sup>C (programmed by BUCKxVOUT[7:0]) after they have been enabled, the buck control circuit changes the output voltage target directly to the final value. The buck output voltage then increases as a function of the output capacitance and load. In such a case, the overvoltage comparator provides an overvoltage assertion, which if not masked by BUCKx\_OV\_M, causes a power-down sequence. If such a use case is foreseen, set the mask bits first and then change the output voltage. Alternatively, change output voltage in small steps. Note that even if the mask bit is set, the corresponding interrupt bit is still set.

- A sudden load release with a high slew rate and magnitude might cause a momentary overshoot on the output of the buck that can trip the OV comparator output. If such use cases are expected, set the OV threshold as high as allowed.

- All the above conditions have associated status bits in the BUCK\_STAT register that provide a real-time status of the conditions.

#### **Enable and Power Mode Control**

- Enable or disable BUCK1/2 either by the flexible power sequencer or by I<sup>2</sup>C.

- The BUCKxFPS register determines if they are part of the power-up and power-down sequence as well as the master and slot numbers they are assigned to.

- Control whether the buck is in Normal Power mode or Low Power mode with the BUCKxOPMD[1:0] bits in the OPMD1 register.

- By setting BUCKxOPMD[1:0] = 0b00, the buck regulator is disabled.

- The buck can be configured to dynamically transition to low power mode when the PMIC transitions to the DevSlp state.

- The buck can also be forced to transition to low-power mode through an I<sup>2</sup>C command. See the Buck and LDO Decode Logic in the Flexible Power subsection in the Global Resources section.

# **Active Discharge Resistor**

BUCK1/2 have an active-discharge resistance that can be enabled and disabled with BUCKxADDIS in the BUCKxCNFG2 register. Enabling the active discharge feature helps ensure a complete and timely power down of all system peripherals. The default condition of the active-discharge resistor feature is enabled, such that when the buck converter is disabled, an internal  $100\Omega$  discharge resistor is connected to the output to discharge the energy stored in the output capacitor. When the buck converter is enabled, the discharge resistor is disconnected from the output.

Maxim Integrated Page 27 of 83

# Buck Regulators (BUCK3—3A Output)

BUCK3 is a step-down converter with the following:

- Programmable output voltage from 0.26V to 1.52V in 10mV steps

- Programmable Low Power mode (LPM) to enable efficient low power PMIC states

- Programmable brownout and overvoltage comparators

# **Setting Output Voltage**

Set the output voltage with BUCK3VOUT[6:0] in the BUCK3CNFG1 register. For example, to set BUCK3 to output 0.8V, set BUCK3CNFG1 = 0x37.

# **Active Discharge**

To enable a  $100\Omega$  active discharge resistance from the output to ground while the buck is disabled, set BUCK3ADDIS = 0.

### **Output Monitoring**

BUCK3 has multiple ways of ensuring the health of its output:

- There is a programmable brownout monitor that sets an interrupt flag (BUCK3\_UV\_I) in the BUCK\_INT register when the output voltage falls below the programmed brownout threshold.

- To allow the brownout on the output of the buck to initiate a power down sequence, clear the BUCK3\_UV\_M bit.

- When the buck is first enabled, either through I<sup>2</sup>C or by the sequencer, the brownout condition is not asserted until the soft-start is complete. However, if the output capacitance is large enough, the soft-start process completes before the output reaches the rising UV threshold, so the UV interrupt would get set, although the output would eventually rise above the UV threshold.

- However, when the output voltage target is increased through I<sup>2</sup>C (write to BUCK3VOUT[6:0]) and the buck converter is in the process of performing the controlled ramp to the new target, a brownout condition is not triggered until the controlled ramp is complete.

- There is a programmable overvoltage monitor that sets an interrupt flag (BUCK3\_OV\_I) when the output voltage rises above the programmed overvoltage threshold.

- To allow the overvoltage on the output of the buck to initiate a power-down sequence, clear the BUCK3\_OV\_M bit.

- However, when the output voltage target is decreased through I<sup>2</sup>C (write to BUCK3VOUT[6:0]) and the buck converter is performing the controlled ramp to the new target (if BUCK3FSREN = 1), an overvoltage condition is not triggered until the controlled ramp is complete. Note that if the controlled ramp for decreasing output voltage target is disabled (BUCK3FSREN = 0), then the overvoltage condition is triggered and could cause a power-down sequence if unmasked (BUCK3\_OV\_M = 0). If this situation is expected, mask it by setting BUCK3\_OV\_M.

- All the above conditions have associated status bits in the BUCK\_STAT register that provide a real-time status of the condition.

Maxim Integrated Page 28 of 83

## **Enable and Power Mode Control**

Enabled BUCK3 either by the flexible power sequencer or by I<sup>2</sup>C.

- The BUCK3FPS register determines if it is part of the power-up and power-down sequence as well as the master and slot numbers that it is assigned to.

- Control whether the buck is in Normal Power mode or Low Power mode with the BUCK3OPMD[1:0] bits in the OPMD1 register.

- By setting BUCK3OPMD[1:0] = 0b00, the buck regulator is disabled.

- The buck can be configured to dynamically transition to Low Power mode when the PMIC transitions to the DevSlp state.

- The Buck can also be forced to transition to Low Power mode through an I<sup>2</sup>C command. See the Buck and LDO Decode Logic in the Flexible Power subsection in the Global Resources section.

Maxim Integrated Page 29 of 83

# Load Switch Driver (LSW1/2)

There are two dedicated external load-switch controllers. When the inrush feature is disabled (OTP\_INRUSH\_DISABLE = 1) in the OTP\_2B\_INRUSH register, the inrush block can be configured to be the third Load Switch controller by setting the LSW\_OTP\_SEL flag in the INRUSH\_OPTION register. In this configuration, the inrush block pins INR\_DRV and INR\_OUT function as LSW3\_DRV and FBLSW3, respectively. The soft-start circuit to minimize inrush current is also programmable.

# **Input Selection**

For the load-switch controllers to report POK status at the output (measured by the FBLSWx pin), select the inputs to each of the load switch controllers with the CNFG\_LSWx register.

- Provided LSWx\_INP\_EXT = 0, select among three internal buck regulators with LSWx\_INP\_SEL[1:0].

- If LSWx\_INP\_EXT = 1, the input to the load switch is assumed to be VSYS.

# **Output Drive**

- Upon enabling either through I<sup>2</sup>C or by the sequencer (see the Load Switch Power Mode Control section), the load switch controller's output stage drives the gate of the switch in a controlled manner using an internal oscillator. See the Load Switch Power Mode Control section for details on enabling/disabling.

- Program the frequency of this oscillator through LSWx\_DRV\_FREQ[2:0], where x = 1,2. For LSW3, the oscillator frequency is set by OTP\_INR\_FREQ[2:0] in the OTP\_2B\_INRUSH register.

- Different frequencies result in varying gate drive strengths, resulting in differing inrush currents through the switch.

## **Programming Soft-Start**

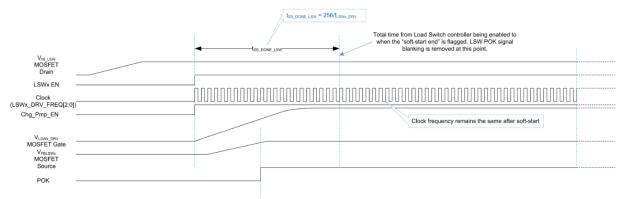

Program the soft-start of the load switch by setting the drive frequency (LSWx\_DRV\_FREQ[2:0]) and following the equation:

$$t_{SS\_DONE\_LSW} = \frac{256}{f_{LSWx\_DRV}}$$

Refer to the Load Switch Controller Timing Diagram for a visual representation of the soft-start.

Maxim Integrated Page 30 of 83

# Load Switch Controller Timing

The following diagram shows the load switch controller's start-up timing while driving an external load switch.

Figure 7. Load switch start-up timing: Soft-start behavior of a load switch.

Maxim Integrated Page 31 of 83

# Load Switch Driver (LSW3)

When the inrush feature is disabled (OTP\_INRUSH\_DISABLE = 1) in the OTP\_2B\_INRUSH register, the inrush block can be configured to be the third Load Switch controller by setting LSW3\_ENABLE = 1 in the INRUSH\_OPTION register. In this configuration, inrush block pins INR\_DRV and INR\_OUT function as LSW3\_DRV and FBLSW3, respectively.

# **Input Selection**

For the load switch controllers to report POK status at the output (measured by the FBLSWx pin), each of the load switch controllers features programmable input selection.

- Provided LSWx\_INP\_EXT = 0, select among the three internal buck regulators with LSWx\_INP\_SEL[1:0] in the CNFG\_LSW3 register.

- If LSWx\_INP\_EXT = 1, the input to the load switch is assumed to be VSYS.

# **Output Drive**

The load switch controller comprises an integrated charge pump that uses the voltage at SYS to drive the gate of the external N-channel MOSFET such that in steady state the external MOSFET is driven to saturation (completely ON).

- Upon enabling either through I<sup>2</sup>C or by the sequencer (see the Load Switch Power Mode Control section), the load switch controller's output stage drives the gate of the switch in a controlled manner using an internal oscillator.

- Program the frequency of this oscillator through OTP\_INR\_FREQ[2:0] in the OTP\_2B\_INRUSH register.

- Different frequencies result in varying gate drive strengths, which results in differing inrush currents through the switch.

## **Programming Soft-Start**

• Program the soft-start of the load switch by setting the drive frequency (OTP\_INR\_FREQ [2:0]), which follows the equation:

$$t_{SS\_DONE\_LSW} = \frac{256}{f_{LSWx\_DRV}}$$

Refer to the Load Switch Controller Timing Diagram for a visual representation of the soft-start.

Maxim Integrated Page 32 of 83

# Linear Regulator

The device includes one on-chip LDO linear regulator. Programmability includes:

- On/Off control

- Output voltage

- Low Power mode

# Setting the Output Voltage

Program the output voltage of the LDO by setting the VOUT\_LDO[6:0] bits in the LDOCNFG1 register. The voltage can range from 0.8V to 3.95V in 25mV increments.

# **Active Discharge Resistor**

The LDO has an active-discharge resistance that can be enabled and disabled with ADE\_LDO in the LDO\_CNFG1 register. Enabling the active discharge feature ensures a complete and timely power down of all system peripherals. The default condition of the active-discharge resistor feature is enabled such that whenever  $V_{SYS}$  is below  $V_{SYSUVLO}$ , the LDO is disabled with its active discharge resistors turned on. When  $V_{SYS}$  is less than 1.0V, the NMOS transistor controlling the active discharge resistor loses its gate drive and becomes open. See the Register Description section for additional details.

#### **Enable and Power Mode Control**

Enable and disable the LDO either by the flexible power sequencer or by I<sup>2</sup>C.

- The LDOFPS register determines if it is part of the power-up and power-down sequence as well as the master and slot numbers that it is assigned to.

- Control whether the linear regulator is in Normal Power mode or Low Power mode with the LDOOPMD[1:0] bit in the OPMD2 register control.

- By setting LDOOPMD[1:0] = 0b00, the buck regulator is disabled.

- The LDO can be configured to dynamically transition to Low Power mode when the PMIC transitions to the DevSlp state.

- The LDO can also be forced to transition to low-power mode through an I<sup>2</sup>C command. Refer to the Buck and LDO Decode Logic in the Flexible Power subsection of the Global Resources section.

Maxim Integrated Page 33 of 83

# I<sup>2</sup>C Serial Communications Interface

The MAX77752 features revision 4.0 of the  $I^2C$ -compatible, 2-wire serial interface consisting of a bidirectional serial data line (SDA) and a serial clock line (SCL). The MAX77752 acts as a slave-only device relying on the master to generate a clock signal. SCL clock rates from OHz to 3.4MHz are supported. Optional resistors (24 $\Omega$ ) in series with SDA and SCL protect the device inputs from high-voltage spikes on the bus lines. Series resistors also minimize cross-talk and undershoot on bus signals. For additional information on  $I^2C$ , refer the  $I^2C$ -bus specification and user manual that is available from NXP (document title: **UM10204**).

#### I<sup>2</sup>C Interface Power

The MAX77752's I²C interface derives its power from  $V_{IO}$ .  $V_{IO}$  accepts voltages from 1.7V to 3.6V ( $V_{VIO}$ ). Cycling  $V_{IO}$  does not reset the I²C registers. When  $V_{IO}$  is less than  $V_{IO\_UVLO}$  and  $V_{SYS}$  is less than VSYSUVLO, SDA, and SCL are high-Z. Ensure the supply at  $V_{IO}$  is at the nominal voltage for at least  $2\mu$ s before an I²C transaction is sent to the MAX77752. Also ensure the configurations of the power-up sequence do not cause a situation that violates this.

# I<sup>2</sup>C Acknowledge Bit

The MAX77752 issues an ACK for all register addresses in the possible address space even if the register does not exist.

# I<sup>2</sup>C Clock Stretching

In general, the master device is responsible for generating the clock signal for the  $I^2C$  bus. The  $I^2C$  specification allows slow slave devices to alter the clock signal by holding down the clock line. The process in which a slave device holds down the clock line is typically called clock stretching. The MAX77752 does not use any form of clock stretching to hold down the clock line.

#### I<sup>2</sup>C General Call Address

The MAX77752 does not implement the  $I^2C$  specification's "general call address." If the MAX77752 sees the general call address (0b0000\_0000) it does not issue an acknowledge.

#### I<sup>2</sup>C Device ID

The MAX77752 does not support the I<sup>2</sup>C Device ID feature.

# I<sup>2</sup>C Watchdog Timer

The MAX77752 contains an I<sup>2</sup>C watchdog timer to ensure reliable operation of the I<sup>2</sup>C bus. This I<sup>2</sup>C watchdog timer helps the system recover from I<sup>2</sup>C bus hang-ups that occur when devices on an I<sup>2</sup>C bus operate out of sync from each other due to noise, poor system design, or poor IC design. In many cases, I<sup>2</sup>C bus hang-ups can be cleared by the master. The master can clear the I<sup>2</sup>C bus by issuing nine consecutive clock pulses. In all known cases, the MAX77752 I<sup>2</sup>C state machine is cleared whenever the master issues nine consecutive clock pulses. However, to account for unforeseen system issues, the I<sup>2</sup>C watchdog timer serves as a back-protection method for I<sup>2</sup>C bus hang-ups. With the I<sup>2</sup>C watchdog timer disabled, the MAX77752 meets the OHz SCL frequency requirements in the I<sup>2</sup>C specification (UM10204). In many cases, this OHz capability is not needed. Activating the I<sup>2</sup>C watchdog timer defeats the OHz specification of I<sup>2</sup>C. Enable the I<sup>2</sup>C watchdog timer with the WD\_EN bit in I2C\_CTRL1 register. With the I<sup>2</sup>C watchdog timer enabled, the MAX77752 monitors the time between consecutive SCL

Maxim Integrated Page 34 of 83

edges. If this time exceeds the  $I^2C$  watchdog timer period of 35ms, the MAX77752  $I^2C$  state machine is reset. If a STOP condition is detected when the watchdog timer is running, the timer is reset until the next START condition. The  $I^2C$  watchdog timer also generates an interrupt signal that can be used at top-level to indicate an  $I^2C$  watchdog timer interrupt. Any SCL line transition (rising edge or falling edge) clears the watchdog timer. This SCL line monitoring capability prevents any unexpected wrong reset of the  $I^2C$  controller during very long burst mode transactions.

# I<sup>2</sup>C Communication Speed

The MAX77752 is compatible with four communication speed ranges as defined by the  $I^2C$  4.0 specification:

- OHz to 1MHz (Fast Mode Plus)

- OHz to 3.4MHz (High-Speed Mode)

The MAX77752 does not support the Ultra Fast mode data rate (5Mbit/s) defined in the  $I^2C$  4.0 specification. Operating in standard mode, fast mode, and fast mode plus does not require special protocols. The main consideration when changing the bus speed through this range is the combination of bus capacitance and pull-up resistors. Higher time constants created by the bus capacitance and pull-up resistance (C\*R) slow the bus operation. Therefore, when increasing bus speeds, the pull-up resistance must be decreased to maintain a consistent time constant. See the "pull-up resistor sizing" section of the  $I^2C$  4.0 specification (UM10204) for detailed guidance on the pull-up resistor selection. In general, for bus capacitances of 200pF, a 100kHz bus needs  $5.6k\Omega$  pull-up resistors, a 400kHz bus needs approximately  $1.5k\Omega$  pull-up resistors, and a 1MHz bus needs  $680\Omega$  pull-up resistors. When the open drain bus is low, the pull-up resistor is dissipating power, lower value pull-up resistors dissipate more power ( $V^2/R$ ).

Operating in high-speed mode requires some special considerations. For a full list of considerations, see the  $I^2C$  4.0 specification (UM10204). The major considerations with respect to the MAX77752 device are:

- The I<sup>2</sup>C bus master must use current source pull-ups to shorten the signal rise times.